#### 8-Bit 400 Ms/s Folding ADC

Ralph S. Li Jimmy T. Yu Peter J. Caralis

### Overview

Folding Architecture

#### Implementation

- Top Level Diagram

- Folder

- Interpolation

- Comparator

- Course ADC

- Synchronization

- Performance

- Conclusion

# **Folding Architecture**

- Moderate Resolution 6-12 Bits

- High Speed

- Fewer Comparators than Flash

- Less Area

- Lower Power Consumption

- Applications: Communications, LANs, Flat Panel Displays

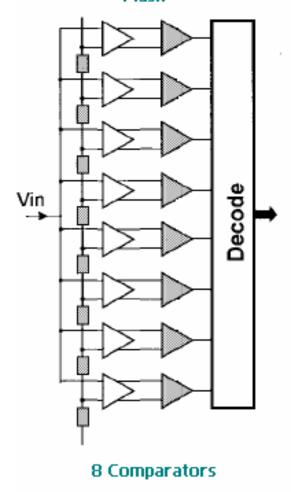

### Flash vs. Folding

Flash

Folding

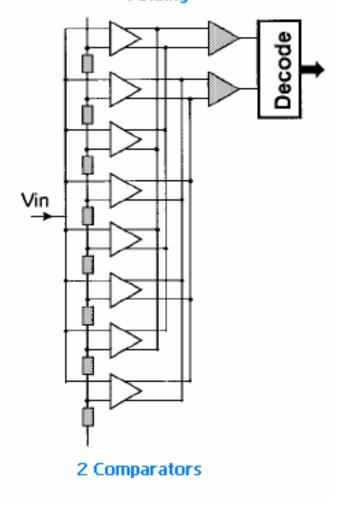

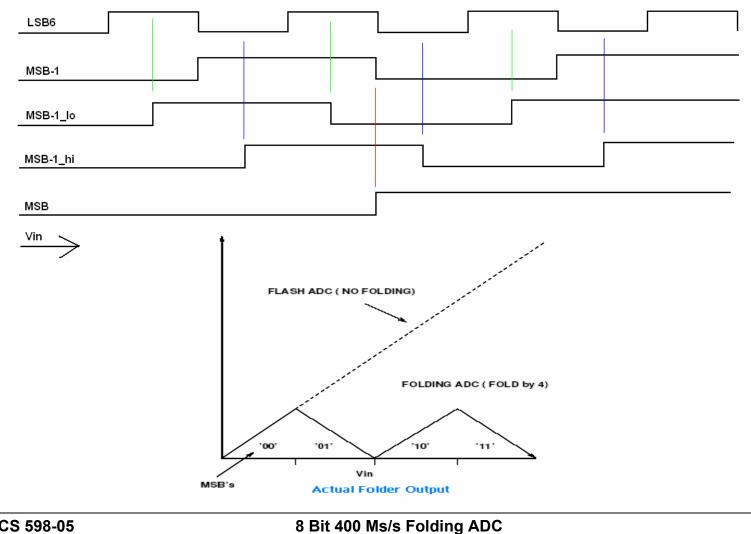

## **Folding Concepts**

### **Folding Concepts**

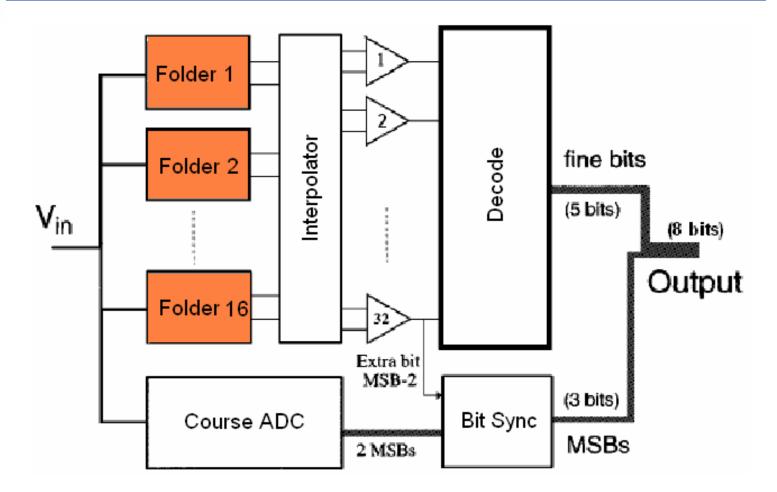

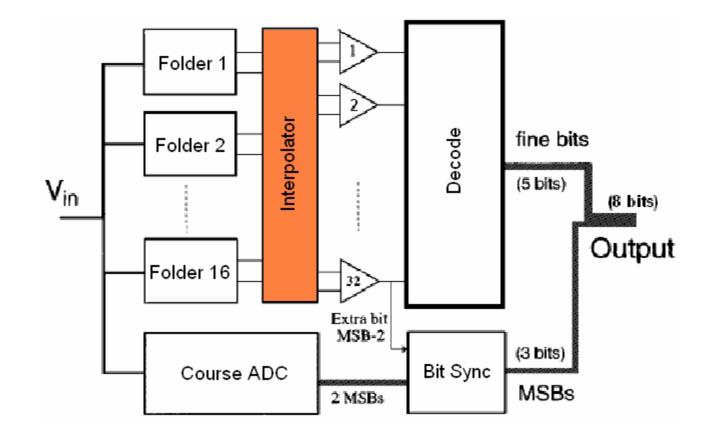

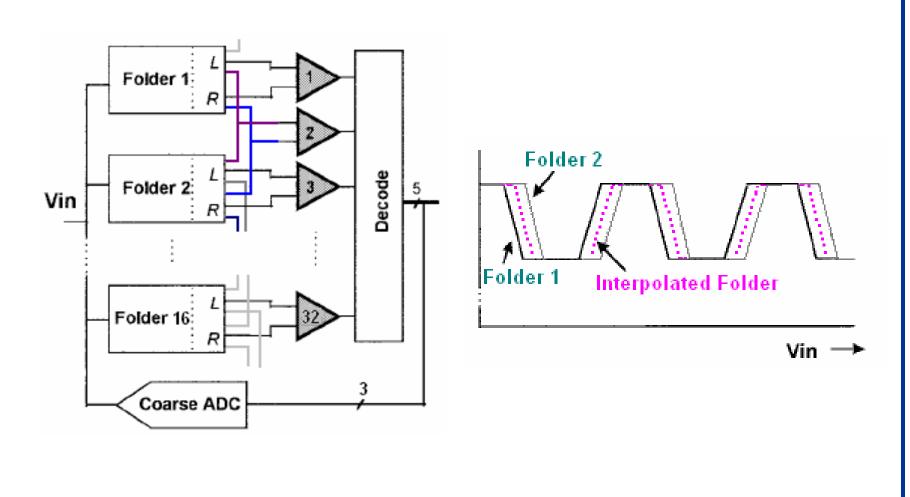

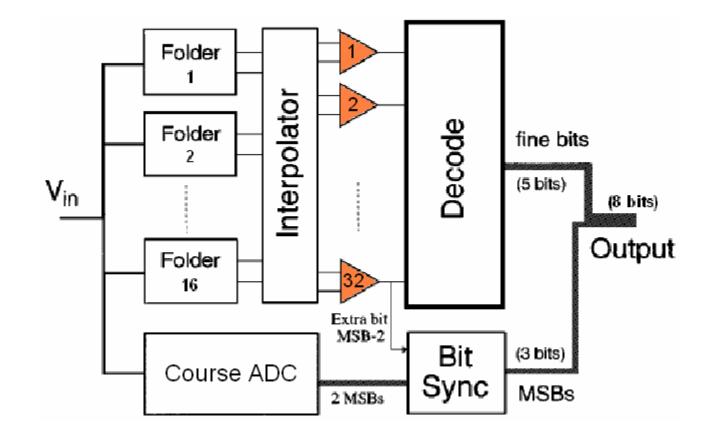

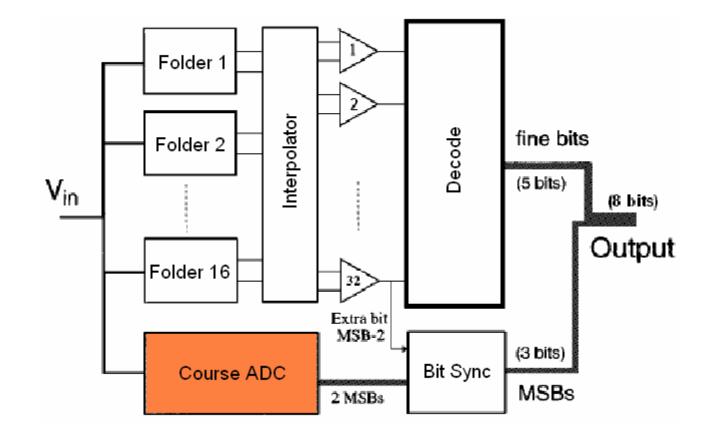

### **Top Level Diagram**

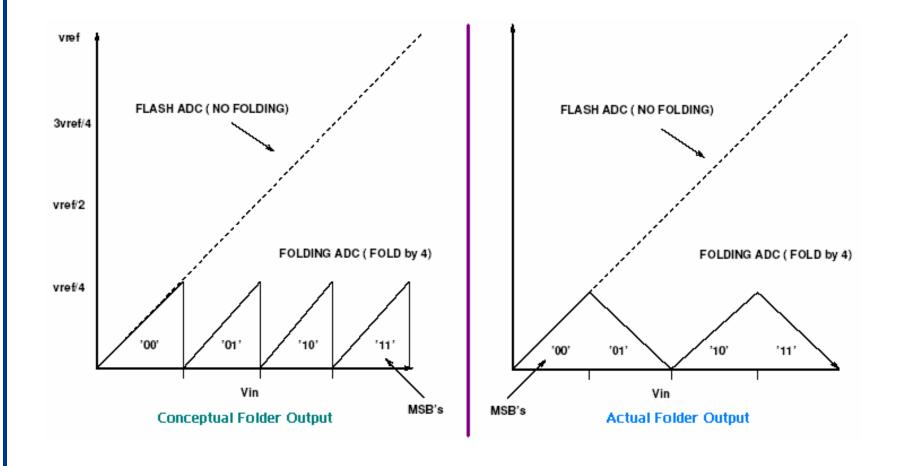

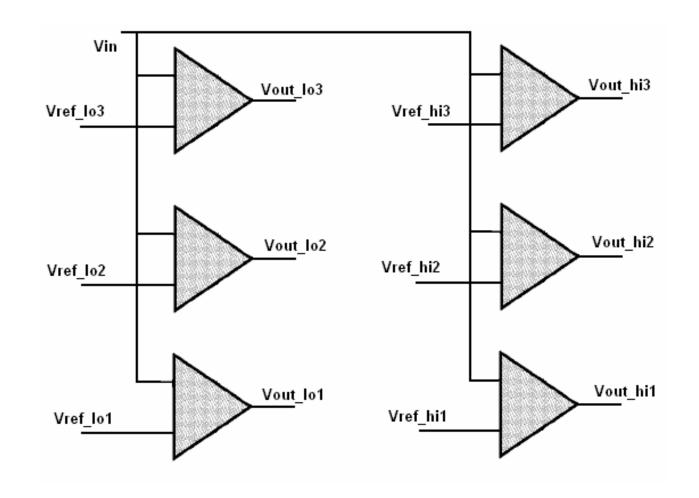

#### Folders

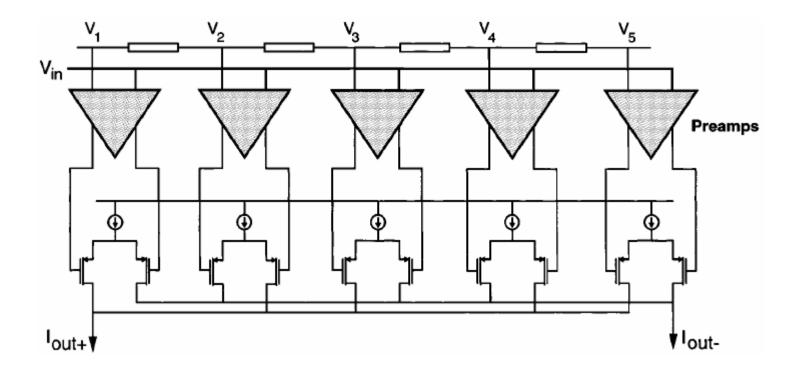

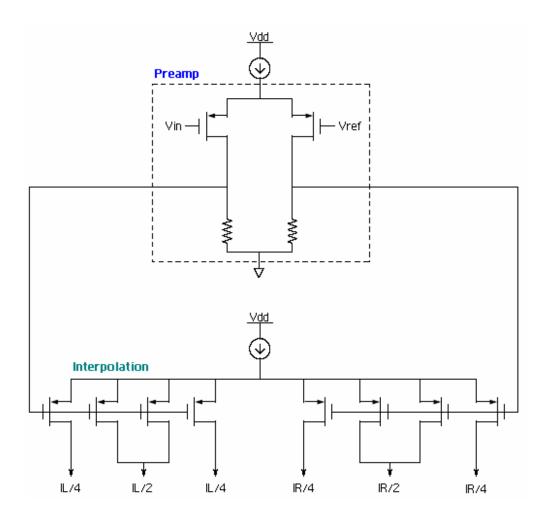

### Interpolation

### Interpolation

### Interpolation

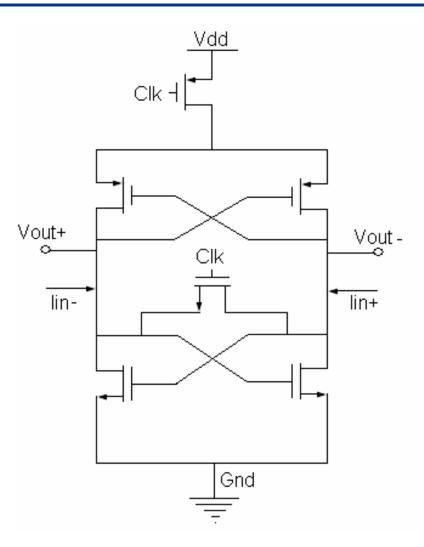

### Comparator

### Comparator

#### **Course ADC**

### Course ADC

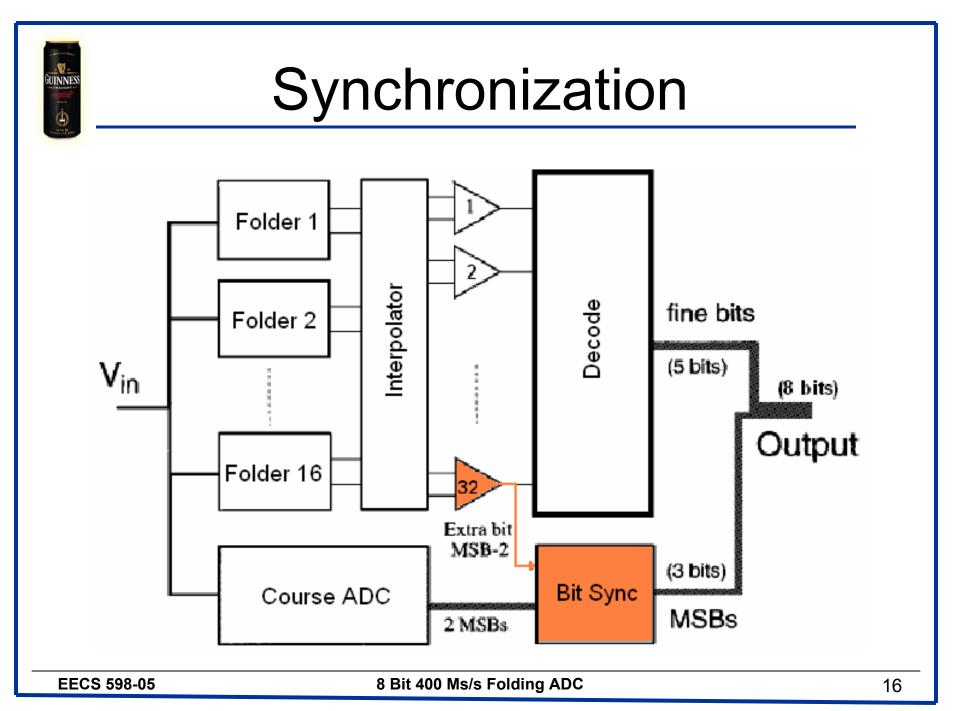

### Synchronization

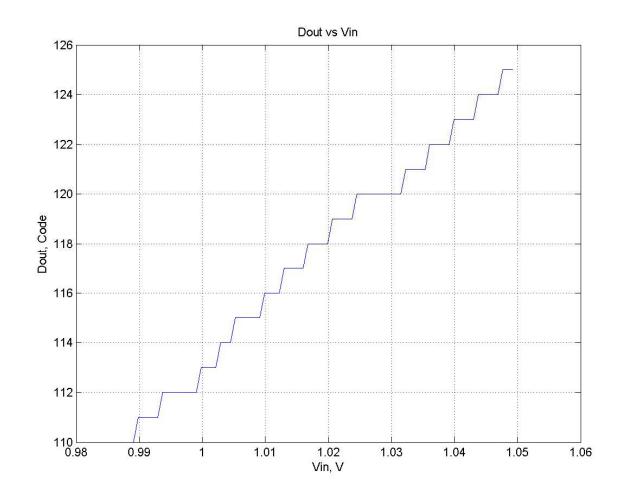

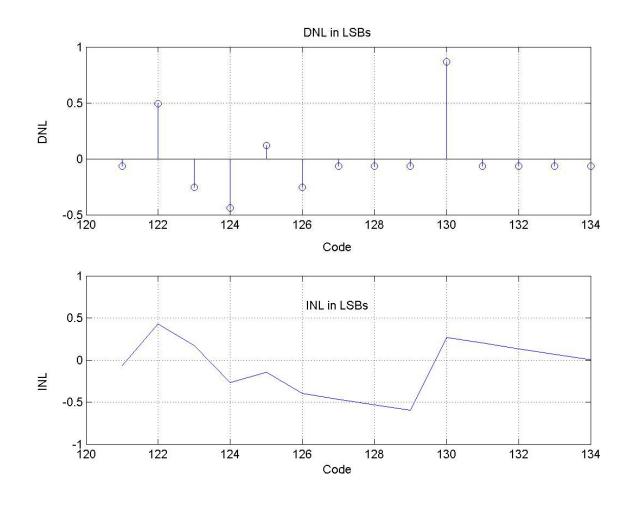

### Performance

| Resolution    | 8 bits      |

|---------------|-------------|

| Sampling Freq | 400 MHz     |

| Input Range   | 0.5V – 1.5V |

| SNDR          | n/a         |

| ENOB          | n/a         |

| DNL           | 0.87 LSB    |

| INL           | 60 LSB      |

| Power         | 238 mW      |

### Performance

### Performance

### Conclusion

- Folding technique greatly reduces the number of comparators.

- Interpolation eliminates half of the folders.

- Synchronization between course and fine removes errors caused by metastability.

- Folding architecture is very effective for achieving a good resolution at low power and high speed.